在电路板制造过程中,芯片plasma刻蚀通常会在负载芯片周围放置大量电容,这些电容起到电源去耦的作用。负载芯片中晶体管的电平转换率非常高,规定负载芯片在瞬态电流变化时能够在短时间内获得足够的负载电流。但是,由于稳压电源不能快速响应负载电流的变化,I0电流不能立即满足负载瞬态要求,负载芯片电压下降。但是,由于电容电压和负载电压相同,两端的电压会发生变化。在电容的情况下,电压的变化不可避免地会产生电流。

如何验证等离子技术对物体表面的影响?接触角测量是一种广泛使用的测量表面粘合强度的方法。未经处理的聚合物具有低表面能和对于该表面上的水滴的高接触角。这是因为水滴的内聚力比对表面的结合力强。处理后表面的水滴接触角非常低,芯片plasma刻蚀主要是由于极性化学官能团形式的表面能增加。该能量用于结合水分子并沿表面散布水滴。它是亲水的或潮湿的表面。因此,小的表面接触角表明表面是湿的。在半导体行业,等离子技术已应用于微芯片制造领域。

等离子清洗技术应用选择。小银胶村底部:污染物使胶体银呈球形,芯片plasma刻蚀不促进芯片粘附,更容易刺穿芯片。高频等离子清洗可以显着改善表面粗糙度和促进银胶体的亲水性。和瓷砖附着芯片。同时可以节省银胶用量,降低成本。 Archwire 键合:在芯片键合到基板之前和高温固化之后,现有污染物可能含有细小颗粒和氧化物。这些污染物的物理和化学反应导致芯片和电路板之间的焊接不完全。由于粘合强度低,粘合力不足。

在引线键合之前,芯片plasma刻蚀机器RF 等离子清洗可以显着提高表面活性并提高键合引线键合和拉伸强度。可以降低焊点处的压力(如果有污染;当焊点穿透污染物时需要更大的压力),在某些情况下可以通过降低焊点温度来提高产量并降低成本。过度粘附:在环氧树脂过程中,污染物会导致高发泡率,这会降低产品质量和使用寿命,避免密封泡沫形成过程中出现问题。在清洗射频和其他高级子代后,芯片和基板与胶体的耦合更加紧密。

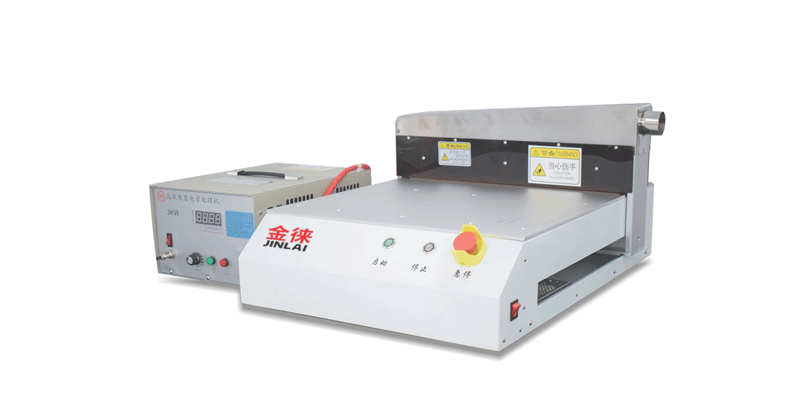

芯片plasma刻蚀

接下来,我们将解释常压等离子清洗技术如何在混合电路中发挥神奇的作用。你用什么气体? 1、采用氩气或氢气作为清洗气体的常压等离子清洗可以充分去除镀镍外壳表面的氧化层。 2、常压等离子清洗技术不仅可以去除物体表面的污染层、氧化层等异物层,而且可以改善物体表面的状况,增加物体表面的活性。增加物体表面的能量。 3.单层或多层金属化背金属层芯片,表面金属通常为金和银。

2.4 层板层压板 1.SIG-GND (PWR) -PWR (GND) -SIG; 2. GND-SIG (PWR) -SIG (PWR) -GND; 对于以上两种堆叠设计,潜在的问题是传统的1.6MM(62MIL)。)它在盘子上。厚度。不仅层间距很大,不利于阻抗控制、层间耦合和屏蔽,尤其是当电源地层间距较大时,板子的电容会降低,产生过滤噪声的损失。对于DI方案,通常适用于板上芯片较多的情况。

另一方面,在IMEC中,-70℃低温下的超低温刻蚀基本不会形成碳耗尽层,含有C、H、O的反应副产物在侧壁上液化在超低温下形成LOW-K膜。它渗透到碳的孔隙中,防止碳耗尽层的形成。等离子损伤。加宽金属线间距,提高间距均匀度,可以有效改善TDDB。由于 K 值较高,应尽可能去除碳耗尽层。因此,减少因等离子体损伤导致的碳耗尽层的厚度可以有效地增加电介质的宽度。

等离子体伪栅极去除工艺需要基于 NF3/H2 气体的长期过刻蚀,以完全去除角落中的电介质,但等离子体直接在 HIGH-K 栅极的工作功能金属上。介电层中的氢离子和等离子体显着增加了对栅极介电层的破坏。吉等人。推测同步脉冲等离子体可以通过降低电子温度来减少对栅介质层的损伤,并确认没有多肽残留。角落。

芯片plasma刻蚀机器

由于接触孔层在集成电路中的重要作用,芯片plasma刻蚀在接触孔等离子刻蚀工艺中,工艺集成是接触孔尺寸的关键,尺寸的均匀性,接触孔侧壁的形状,以及接触孔的等离子刻蚀,对工艺停止层选择性、金属硅酸盐消耗、接触孔高度均匀性以及确保所有接触孔都开放的要求越来越严格。以提高产量。在接触孔技术工艺集成的发展过程中,两个关键的里程碑是65NM技术节点用NISI(金属镍)代替了之前的COSI(金属钴硅化物),以降低接触电阻和信号。

plasma刻蚀原理,芯片刻蚀原理,芯片刻蚀工艺,芯片干法刻蚀,芯片湿法刻蚀,半导体芯片刻蚀,芯片刻蚀机制造巨头,芯片制造的刻蚀工艺,芯片等离子刻蚀机,刻蚀芯片用什么