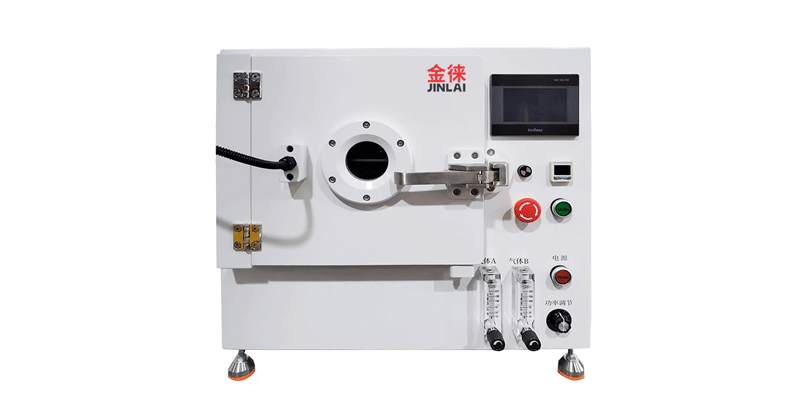

等离子体清洗机和等离子体表面处理器的相变存储器下电极接触孔的蚀刻过程:在相变存储器的存储单元中加热器和贯穿;下电极接触的大小对器件性能至关重要。更小的尺寸意味着更高的电流密度,氮化硅薄膜亲水性更高的加热效率,更小的相变材料面积在较低的电极接触。以GST为相变材料的叶片形氮化硅电极接触的结构和过程,可以形成沿位置线方向尺寸小于20nm的低电极接触。

氮化硅薄膜的亲水性.jpg)

等离子处理器复合氮化工艺提高扩散速率的机理分析 调质后零件表面组织为回火索氏体,氮化硅薄膜是亲水性零件表面强度更高,芯部塑性更好。后续的微加工工艺旨在去除零件表面淬火和回火后的氧化皮,为后续工艺做准备。采用渗入前零件表面感应淬火提高渗入率,表面淬火后零件表面组织为马氏体和残余奥氏体,均为组织缺陷。位错等缺陷,这些缺陷为后续的冷氮渗透技术提供能量和结构支撑。

& EMSP; & EMSP; (2)离子氮化& EMSP; & EMSP;离子氮化是业界应用最广泛的成熟离子热处理工艺[1-3]。通过调整工艺参数(电压、电流、炉内气体压力、温度、时间、工作气体成分等),氮化硅薄膜的亲水性很容易得到纯扩散层、单相、复合层等。离子渗氮技术的关键是如何根据其特性合理选择工艺参数,并结合模具的相关使用条件,以获得所需的最佳氮化层。

因此,氮化硅薄膜是亲水性对于聚酰亚胺薄膜芯片,需要控制等离子清洗的次数,即进行一次等离子清洗。氮化硅钝化膜芯片可以用等离子清洗多次,而不会出现环状皱纹。对等离子清洗对芯片电性能影响的研究表明,随着等离子清洗功率和时间的增加,78L12芯片的输出电压有增加的趋势。等离子清洗过程中芯片输出电压的变化是一个可逆过程,在退火和上电老化过程中,输出电压逐渐下降恢复平衡。

氮化硅薄膜的亲水性

氮化硅薄膜的亲水性.jpg)

然而,虽然工件表面的高温足以促进化学反应的结合,但也足以使工件内部原有的性能发生不必要的变化。为了恢复材料内部的性能,还需要进行后续的热处理。将两个电极置于具有适当压力分布的混合气体中,并在它们之间施加电压,产生辉光放电,通过氮等离子体表面处理进行等离子体氮化处理。电极或阳极接地到真空盖上。另一个是阴极。是离子氮化的工件。当对工件进行氮化处理时,工件相对于地面真空罩是负的。将二极管电路连接到变压器电源。

因此,如果发现等离子体表面垫圈的侧壁蚀刻的主蚀刻步骤的终点监测被暴露,则立即停止蚀刻并切换过蚀刻步骤。在主蚀刻步骤中残留的氮化硅膜通过过蚀刻步骤被蚀刻掉,同时停止在氧化硅膜上,以防止损坏下面的硅衬底。过蚀刻步骤通常使用 CH3F 或 CH2F2 和 O2 气体的组合。 CH3F 气体分解为 CHX 和 F. + H。等离子体中的撞击离子会破坏 SI-O 键。

氮化硅薄膜用于制造新的功能性、多功能、可靠的器件和等离子表面处理,其性能高度依赖于薄膜的制造条件。等离子化学气相沉积(简称PECVD)具有沉积温度低(<400℃)、沉积膜针孔密度低、均匀性高、台阶覆盖率好等优点。 PECVD氮化硅薄膜技术广泛应用于半导体器件和集成电路的开发、芯片固定化膜的制作、多层布线之间的介质膜的制造,并已发展为大规模和超大规模集成。

由于是放热反应,CHx很容易与-Si-N键结合,产生·CN+·H,因此等离子表面清洗机蚀刻反应在氮化硅上很活跃。与此相反,在氧化硅膜层上形成很厚的高分子聚合物,阻止了反应的进一步进行,一般情况下可以通过工艺优化得到高于10的选择比,表3.8列出了不同碳氟比条件对介质层及硅的刻蚀速率、选择比及均匀度。侧墙的宽度和高度主要由沉积的膜层的厚度和等离子表面清洗机过蚀刻的程度决定。

氮化硅薄膜的亲水性.jpg)

氮化硅薄膜亲水性

它包括化学热处理(氮化、碳化、金属渗透等)。)表层涂层(低压等离子体涂层、低压电弧涂层、激光再熔融复合等薄膜涂层、物理(气体)相沉积、化学气体相沉积等。分析概念设计中的量体体积。以及非金属涂层技术。本发明用于强化零件或材料表面层的技术赋予部件耐高温、耐腐蚀、耐磨、疲劳、辐射、导电、导磁等新性能。使得本机在高速度、高温、高压、重负荷及腐蚀介质环境中工作更可靠,氮化硅薄膜是亲水性延长使用年限。。